Тема 8. Інтегральні схеми. Основні параметри і характеристики ІС

1. Інтегральні схеми. Основні параметри і характеристики ІС

1.1. Загальна характеристика ІС

1.2. Номенклатура інтегральних мікросхем

1.3. Номенклатура

аналогових ІМС

1.4. Номенклатура та

основні параметри цифрових ІМС

2.1. Логічні елементи на

перемикачах струму з об'єднаними еміттерами

2.2. Логічні

елементи на МДН - транзисторах

3. Тригерні схеми

4. Інтегральні схеми. Основні параметри і характеристики ІС

5. Типи логіки

5.1. Діодно-транзисторна логіка

5.2. Транзисторно-транзисторна логіка

5.3. Транзисторна логіка з безпосередніми зв'язками

3. Типи логіки

3.3. Логічні елементи на перемикачах струму з об'єднаними емітерами

Схемотехніка елементів ЕЗЛ базується на використанні диференціального підсилювача в режимі перемикання струму. Елементи ЕЗЛ з’явилися в 1967 р. і в даний час є над швидкодіючими серед напівпровідникових елементів на основі кремнію. Затримка поширення сигналів в елементах ЕЗЛ зменшилася до субнаносекундного діапазону (порядку 1 нс).

Над швидкодія елементів ЕЗЛ досягається за рахунок використання ненасиченого режиму роботи транзисторів, вихідних емітер них повторювачів, малих амплітуд логічних сигналів (біля 0,8 В). У логічних елементах ЕЗЛ є пара фазний вихід, що дозволяє одночасно отримувати пряме та інверсне значення реалізованої функції. Це дає значне зниження загальної кількості мікросхем в апаратурі.

Особливостями схемотехніки ЕЗЛ та її характеристик є:

![]() можливість об’єднання декількох елементів для

утворення нових логічних функцій;

можливість об’єднання декількох елементів для

утворення нових логічних функцій;

![]() можливість роботи на низькоомному

навантаженні завдяки наявності емітер них повторювачів;

можливість роботи на низькоомному

навантаженні завдяки наявності емітер них повторювачів;

![]() невелике значення роботи перемикання і

незалежність споживаної потужності від частоти перемикання;

невелике значення роботи перемикання і

незалежність споживаної потужності від частоти перемикання;

![]() висока стабільність динамічних параметрів при

зміні температури і напруги живлення;

висока стабільність динамічних параметрів при

зміні температури і напруги живлення;

![]() використання від’ємного джерела живлення і

заземлення колекторних кіл, що зменшує залежність вихідних сигналів від завад у

шинах живлення.

використання від’ємного джерела живлення і

заземлення колекторних кіл, що зменшує залежність вихідних сигналів від завад у

шинах живлення.

До недоліків ЕЗЛ відносять складність схем, значне споживання потужності та труднощі узгодження з мікросхемами ТТЛ і ТТЛШ.

Промисловість випускає ряд серій ЕЗЛ: 100, 137, 138, 187, 223, 229, 700, 500 і К1500. Високі техніко економічні характеристики мікросхем серій 500 і К1500 обумовили їх широке застосування у швидкодіючих цифрових пристроях.Мікросхеми ЕЗЛ серії 500 виготовляють за напівпровідниковою дифузійною пленарно-епітаксіальною технологією. Усі компоненти мікросхеми розташовують в одному кристалі кремнію і ізолюють обернено зміщеними p-n-переходами.

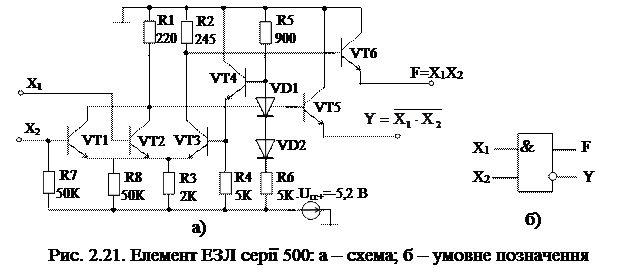

Схема типового логічного елемента ЕЗЛ серії 500 показано на рис. 2.21.

Схема ЕЗЛ вміщує:

· перемикач струму (логічні транзистори VT1, VT2, опорний транзистор VT3, резистори R1, R2, R3);

· джерело опорного зміщення (транзистор VT4, діоди VD1, VD2, резистори R5, R6);

· вихідні емітерні повторювачі (транзистори VT5, VT6).

Напруга на відкритому переході база-емітер кремнієвого транзистора є постійним параметром U*=0,8 В. При аналізі роботи елемента приймаємо домовленість від’ємної логіки: значення лог. 0 відображається високим (з урахуванням знаку) рівнем напруги UН=-0,9 В; значення лог. 1 відображається низьким рівнем напруги UL=-1,7 В. Амплітуда (перепад) логічного сигналу Um= UН- UL= 0,8 В.Опорна напруга перемикача струму розташовується симетрично щодо рівнів двійкових сигналів і визначається як середнє: UОП=-( UН-+UL)/2=-1,3 В.

Якщо хоча б на один із входів подана напруга UН=-0,9 В, то даний транзистор відкривається, на нього перемикається струм ІЕ, що створює на резисторі R1 падіння напруги мінус 0,9 В. При цьому опорний транзистор закритий і на резисторі R2 падіння напруги рівне -0,1 В.

Якщо на усі входи подані рівні UL=-1,7 В, то транзистори VT1, VT2 закриваються, а транзистор VT3 відкривається і на нього перемикається струм ІЕ. У цьому випадку падіння напруги на резисторі R1=-0,1 В, а на резисторі R2 мінус 0,9 В. При цьому на колекторах лівого і правого плеча рівні напруги не відповідатимуть взятому значенню двійкового сигналу. Емітерні повторювачі на транзисторах VT5, VT6 зміщують рівні сигналів, які надходять на їхні бази з лівого і правого плеча перемикача, U*=0,8 В у бік від’ємних сигналів:

UОН=-(U*+0,1)=-0,9 В; UОL=-( U*+0,9)=-1,7 В.

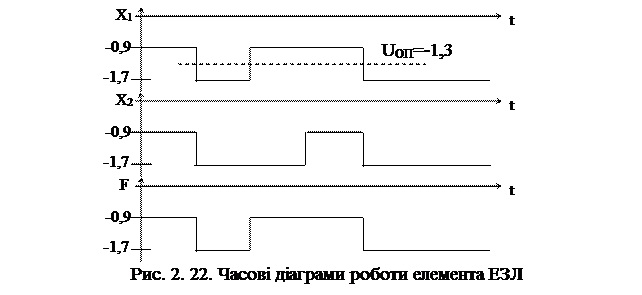

Внаслідок цього рівні вхідних і вихідних сигналів відповідають чинному стандарту. Часові діаграми роботи елемента ЕЗЛ показані на рис. 2.22.

Як випливає з часових діаграм, вхідні і вихідні логічні сигнали змінюються на ±0,4 В щодо опорної напруги.

Підключення від’ємної напруги живлення до емітерного кола і заземлення колекторів забезпечує кращу завадостійкість до перешкод і меншу залежність вихідних сигналів від наведених завад у колі емітера. Опір резистора R3 у декілька разів більший опорів R1 і R2, чим досягається сталість струму ІЕ у плечах перемикача струму. Крім того, співвідношення опорів резисторів R1, R2 і R3 підібрано так, щоб на виході закритого плеча встановлювалась напруга -0,1 В за рахунок протікання струму бази ЕП, а на виході відкритого плеча напруга становила -0,9 В за рахунок протікання струму ІЕ.

Колектори ЕП підключені до окремої шини землі; це пов’язано з тим, що струми повторювачів мають імпульсний характер і вони створюють перешкоди у провідниках, які підводять напругу.

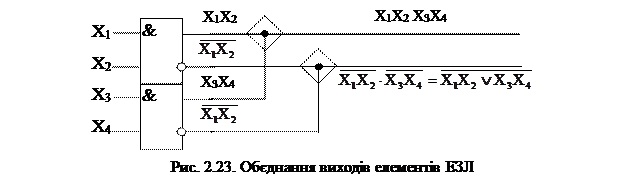

У елементах ЕЗЛ допускається об’єднання виходів, як показано на рис. 2.23. Об’єднання прямих виходів збільшує коефіцієнт об’єднання по І; об’єднання інверсних виходів дозволяє реалізувати функцію НЕ-І-ЧИ.