Тема 8_2. Інтегральні мікросхеми, основні параметри. Логічні елементи і цифрові пристрої.

4. Тригери

Тригер - це пристрій із двома стійкими станами рівноваги, призначений

для запису й зберігання

інформації. Під дією вхідних сигналів тригер

може

перемикатися з одного

стійкого стану в

інший. При цьому напруга на його

виході стрибкоподібно міняється. Число входів залежить від виконуваної

функції.

У цей час в інтегральнім

виконанні виробляється багато тригерів як у вигляді самостійних виробів, так і в складі різних

функціональних обладнань -

лічильників, регістрів, запам'ятовувальних

пристроїв і т.п. Вони мають складні електричні

схеми й різняться числом входів, способами введення

вхідної інформації, реалізованою функцією

переходів, елементною базою,

електричними й тимчасовими

параметрами, конструктивним оформленням і

іншими показниками.

В асинхронних

тригерів є тільки інформаційні (логічні)

входи.

Асинхронні тригери відрізняє властивість

спрацьовувати відразу після зміни

сигналів на входах.

У синхронних

тригерів зміни сигналів на інформаційних

входах ще

недостатньо для спрацьовування. Необхідний

додатковий командний імпульс, який подається на

синхронізуючий, або, як його частіше називають, тактуючий вхід.

Існує кілька типів тригерів.

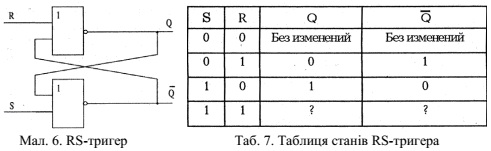

RS-тригер.

RS-тригер утворено двома перехресно зв'язаними елементами АБО-НЕ

або І-НЕ (мал. 6).

RS-тригер

має два виходи Q і Q й два керуючих входи: R (Reset -

скидання) і S (Set - установка). На виходах тригера рівні завжди протилежні:

якщо Q = 1, то Q- = 0, і навпаки.

Для того щоб зрозуміти роботу ланцюга,

припустимо, що вихід Q , вхід R

і S мають низький рівень. Низький рівень виходу Q- подається на один із входів елемента 2. На вході S також низький рівень. На виході елемента 2 високий рівень, який подається на вхід елемента 1, утримуючи його вихід на низькому рівні. Коли на виході Q з'являється низький рівень, говорять, що тригер у вихідному стані (RESET). Він залишається в цьому стані невиразно довго, доти, поки на вхід S

елемента 2 не буде поданий високий рівень. Коли на вхід S елемента 2 буде поданий

високий рівень,

на виході елемента

2 з'явитьсянизький рівень, а цей вихід зв'язаний із входом елемента 1.

Оскільки на вході R елемента 1 низький рівень, на його виході Q низький рівень зміниться на високий і подається на вхід елемента 2, забезпечуючи на виході Q низький рівень. Коли на виході Q високий рівень, говорять, що тригер в одиничному (SET) стані. Він залишається в цьому стані доти, поки на вхід R не

буде

поданий високий рівень, що переводить тригер у вихідний стан.

«Неприпустима»,

або «недозволена», умова має місце, коли одночасно на

обидва входи, R і S, подається високий рівень. У цьому випадку виходи Q й Q- намагаються

перейти в низький стан,

але Q й Q- не можуть бути одночасно в однаковому стані без порушення роботи

тригера. При одночасному відключенні високого рівня із входів R і S обидва виходи намагаються перейти в стан з високим рівнем. Оскільки логічні елементи

небагато відрізняються друг від друга, те один з них перейде в стан з високим рівнем. Це змусить інший елемент перейти в стан з низьким рівнем. У цьому випадку має місце непередбачений режим роботи

й, отже, стан виходів

тригера не може бути визначеним.

Іншим типом тригера є тригер із синхронізуючим входом.

Він

відрізняється від

RS-тригера тим, що для його роботи необхідний додатковий вхід. Третій вхід називається тактовим (або синхронізуючим). На

мал. 7 зображена логічна схема тригера із

синхронізуючим входом і його схематичне

позначення. Сигнал високого рівня на кожному із входів вхідного блоку

тригера активізує тригер, змушуючи його

змінити стан.

Вхідний блок,

називаний «керуючим елементом», направляє тактові імпульси на входи

елементів тригера.

Мал. 7. Логічна схема тригера із

синхронізуючим входом і його схематичне

позначення

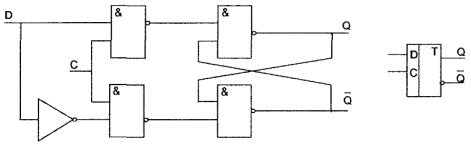

D-тригер.

У цифрових мікросхемах дуже часто застосовують

тригери з єдиним

входом даних D (data), так звані D-тригери. Вони корисні тоді, коли повинен бути збережений тільки один біт даних (1 або 0). На мал. 8 зображені логічна схема й умовна позначка D-тригера.

Він має один вхід для даних і вхід для тактових імпульсів.

Функціональна особливість цього типу тригерів

полягає в тому, що сигнал на виході Q в такті n+1

повторює значення вхідного сигналу Dn в попередньому такті n і

зберігає (запам'ятовує) цей стан до наступного такту.

Інакше кажучи, D-тригер затримує один такт інформацію, що існувала на

вході D. Тому

D-тригер також називають тригером із затримкою.

Мал. 8. D-тригер.

D-тригери, з'єднані разом, утворюють зрушувальні й

регістри пам'яті, які

широко використовуються

в цифрових системах.

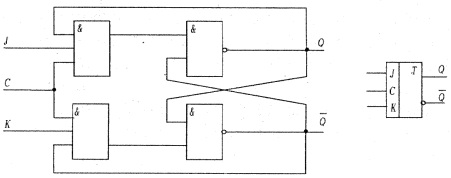

JK-тригер.

Найбільше широко використовуваний тригер -

JK-тригер - має всі особливості тригерів інших

типів. Логічна схема й позначення JK-тригера

показані на мал. 9.

Мал. 9. JK-тригер

JK-тригер при всіх комбінаціях, крім однієї J=K=1, функціонує, як RS

тригер, причому вхід J відіграє роль входу S,

а K – вхід відповідає R-входу. При вхідній комбінації J=K=1 відбувається перекидання тригера й

вихідні сигнали міняють своє значення.

JK-тригери широко використовуються в багатьох цифрових

ланцюгах,

особливо в схемах лічильників. Лічильники

можна знайти майже в кожній

цифровій системі.

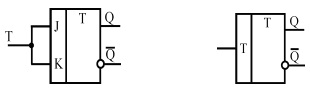

Т-тригер.

Як ми вже відзначали, при вхідній комбінації J

= K = 1 відбувається

перекидання тригера й вихідні сигнали міняють своє значення. Т-тригер

виходить при з'єднанні входів J і K в один рахунковий вхід.

T - тригер (рахунковий) - єдиний вид тригера, поточний стан якого

визначається його ж станом у попередньому такті.

Умовна позначка T

– тригера, назва якого

походить від англійського

слова toggle – перекидатися.

Мал. 10. Схема перетворення

JK-тригера в T – тригер і умовне графічне

позначення T – триггера

Асинхронні й синхронні Т - тригери

в основному застосовуються

для

рахунку числа вхідних імпульсів (звідси й назва - "рахунковий") і

для розподілу частоти

проходження вхідних імпульсів.

Тригери є основними будівельними блоками для побудови послідовних

логічних ланцюгів. Вони можуть бути з'єднані

разом і утворювати лічильники, регістри зсуву й пристрої пам'яті.