Тема 8_2. Інтегральні мікросхеми, основні параметри. Логічні елементи і цифрові пристрої.

| Сайт: | Освітній сайт КНУБА |

| Курс: | Комп'ютерна електроніка |

| Книга: | Тема 8_2. Інтегральні мікросхеми, основні параметри. Логічні елементи і цифрові пристрої. |

| Надрукував: | Гість-користувач |

| Дата: | пʼятниця, 19 квітня 2024, 18:31 |

Опис

1.

Основні параметри великих інтегральних схем

2. Елементи мікросхем

4. Тригери

1. Основні параметри великих інтегральних схем

Розвиток

електроніки визначив удосконалювання характеристик

елементної бази й апаратури у виробництві в наступних

напрямках:

• зменшення габаритів і маси (мініатюризація);

• підвищення надійності за рахунок скорочення сполучних

ліній,

удосконалювання контактних вузлів і взаємного

резервування елементів;

• зменшення споживаної потужності;

• ускладнення завдань і відповідних їм схемних рішень

при одночасному

здешевленні кожного окремого елемента.

Істотні зміни в напівпровідниковій техніці пов'язані,

по-перше, з

переходом до інтегральних мікросхем (ІМС) і, по-друге,

з переходом до

великих інтегральних схем (ВІС).

Інтегральною називають мікросхему з певним

функціональним

призначенням, виготовлену не складанням і розпаюванням

окремих активних і пасивних елементів, а цілком,

у єдиному технологічному процесі.

Прикладами

інтегральних схем можуть служити підсилювачі різних

сигналів, логічні схеми обчислювальної техніки,

генератори синусоїдальних,

імпульсних або пилкоподібних напруг, тригери,

виготовлені як єдине ціле в

об’ємі одного напівпровідникового кристала або в тонких

плівках. Ці схеми

звичайно доповнюють навісними компонентами.

До пасивних елементів електронних схем відносять

резистори,

конденсатори, індуктивні котушки, трансформатори, а до

активних - діоди,

транзистори, тиристори й ін.

Інтегральні мікросхеми містять десятки й сотні пасивних

і активних

елементів. Показник ступеня складності мікросхеми

характеризується числом елементів, що містяться в ній,

і компонентів.

Великі інтегральні схеми також виготовляють в об’ємі

одного кристала.

Вони характеризуються більшою складністю й служать у

якості окремих блоків електронної апаратури,

наприклад запам'ятовувального пристрою, процесора і

т.д.

Ступінь і характер інтеграції елементів мікросхем

визначаються,

насамперед, рівнем технології.

2. Елементи мікросхем

Основою

елементів мікросхем служить p n - - перехід, який можна

формувати різними методами нанотехнологій у

мікрообластях кристала. Він

виконує роль вентиля (діода), декілька p n - - переходів служать

транзисторами, тиристорами, фотоприладами і т.д.

Замкнений зворотною

постійною напругою p n - - перехід виконує роль

конденсатора, зворотний опір p n - - переходу відіграє роль

високоомного резистора. У якості невеликих

опорів

використовують просто ділянки слабо легованого кристала кремнію, від

яких

роблять контактні виводи. Важке завдання одержання котушок

індуктивності

долають різними конструктивними рішеннями.

Багатошарові структури з декількома p n - - переходами одержують,

повторюючи процеси: окиснення, дифузію донорних і

акцепторних домішок у мікрообластях кристала,

формування масок. Складні мікросхеми вимагають

зняття й повторного нанесення нової маски методом

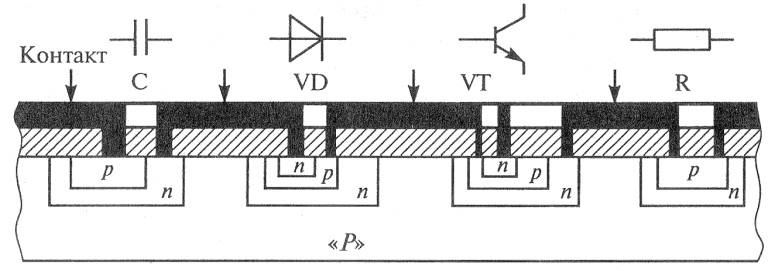

фотолітографії відповідно до топології схеми. На мал. 1

у збільшеному виді представлений підсилювач на

транзисторі.

Мал. 1. Елементи мікросхем

Сформовану мікросхему (МС) покривають плівкою оксиду

кремнію SiO2 ,

у якій витравлюють вікна для золотих контактів. Крім

внутрішньоелементних

(C , VD ,VT , R ) з'єднань, напиляють

контактні майданчики для підведення живлення, вхідних U BX і вихідних U ВИХ сигналів. Контактні майданчики

з'єднують

із зовнішніми виводами за допомогою тонких золотих виводіввводів.

Після МС герметизують, заливаючи епоксидною смолою,

поміщають у

герметичний корпус.

3. Логічні елементи

В основі цифрової електроніки лежить двійкова система числення. Для

запису чисел у двійковій системі потрібні тільки дві цифри - нуль (0) і одиниця (1). Двійкова система числення використовується в цифрових ланцюгах завдяки тому, що двійкові цифри легко представити у вигляді двох напруг - високої й низької.

У логічних ланцюгах можливі два стани - 1 і 0. Стан 1 також називають

високим, щоб указати, що напруга в цьому стані вище, чим у стані 0. Стан 0

також називають низьким, щоб указати, що напруга в цьому стані нижче, ніж у стані 1.

Дані у двійковій системі представляються двійковими цифрами, які

називаються бітами. Біт - двійкова цифра (розряд) (binary digit).

Усе цифрове обладнання сконструйоване з використанням невеликої

кількості основних схем, називаних логічними елементами, які виконують

деякі логічні функції із двійковими даними.

Існують два основні типи логічних схем: схеми прийняття рішень і

пам'ять. Логічні схеми прийняття рішень контролюють двійкові стани входів

і видають вихідний сигнал, заснований на станах входів і характеристиках

логічної схеми. Схеми пам'яті використовуються для зберігання двійкових

даних.

1. Логічні елементи

Розглянемо деякі логічні схеми.

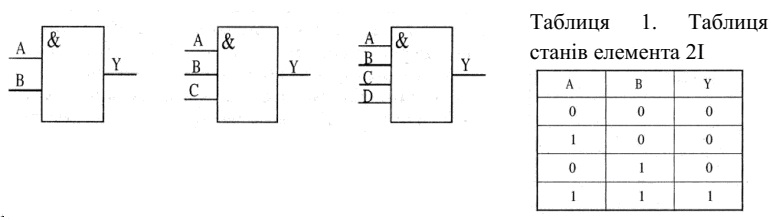

Елемент І - логічна схема, на виході якої 1 з'являється тільки тоді, коли

на всі його входи надходить сигнал 1. Якщо на який-небудь із входів надходить 0, на виході з'являється 0.

На мал. 1 показані стандартні позначення, використовувані для елементів

І. Елемент І може мати будь-яку кількість входів більше одного. Показані

позначення представляють найбільше часто використовувані елементи із двома, трьома й чотирма входами.

Стан і логічний зв'язок між вхідними й вихідними сигналами елемента І

відбиває так звана таблиця істинності (табл. 1), яка показує вихідний стан

двовходового елемента для будь-яких можливих станів входів: А і В - входи; Y- вихід.

Мал. 1. Позначення елементів І

Елемент І виконує операцію

логічного множення, яке відомо як функція І.

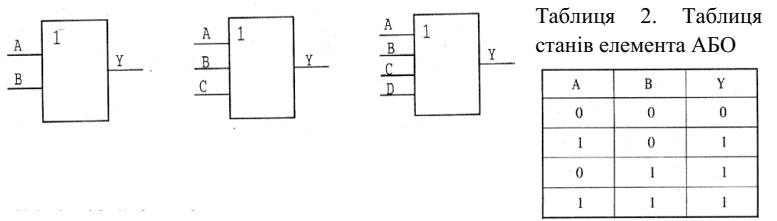

Елемент АБО - це логічна схема, на виході якої з'являється 1, якщо на

будь-який з його входів подано 1. На його виході з'являється 0, якщо на всі його входи

подано 0. Цей елемент, як і елемент І, може мати два

або більш входів.

На мал. 2 показані стандартні позначення,

використовувані для елементів АБО із

двома, трьома й чотирма входами.

Мал. 2. Позначення елементів АБО

Значення на виході елемента АБО із двома

входами наведені в табл. 2: А і

В - входи; Y - вихід.

Елемент АБО виконує логічну операцію

додавання.

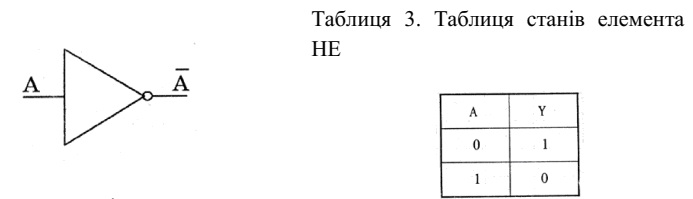

Елемент НЕ виконує функцію, яка називається інверсією. Мета інвертора - зробити стан виходу протилежним стану входу. Якщо на вхід інвертора

поданий високий стан,

або 1, то на виході з'явиться низький стан, або

0. Якщо ж на вхід інвертора подати низький стан, або 0, то на виході з'явиться високий стан, або 1.

Схематичне позначення інвертора показане на

мал. 3.

Мал. 3. Позначення інвертора

Роботу інвертора відбиває табл. 3. Вхід інвертора

позначений A , а вихід

- A (читається «не А»). Риска над буквою

А показує заперечення А. Оскільки

інвертор має тільки один вхід, те можливі тільки два стани входу.

Елемент І-НЕ є комбінацією елементів І і НЕ й

найбільше широко

використовуваною логічною функцією. Це

обумовлене тим, що ці елементи

можуть бути використані для створення деяких

інших логічних елементів.

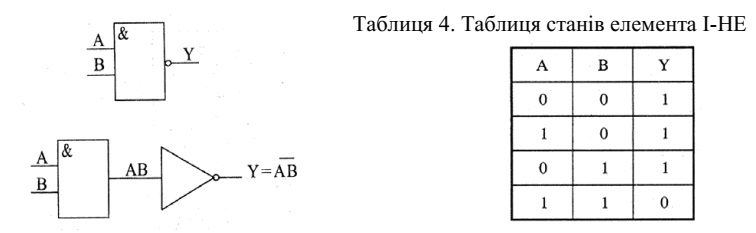

Схематичне позначення елемента І-НЕ, а також

його еквівалентність

послідовно включеним елементу І и інвертору, показані на мал. 4.

Кружечок на виході позначає інвертування функції І.

Мал. 4. Елемент І-НЕ

Нижче наведена таблиця істинності для двухвходового елемента І-НЕ (табл. 4). Помітимо, що вихід елемента І-НЕ є запереченням виходу елемента І.

Подача 0 на будь-який вхід дає на виході 1.

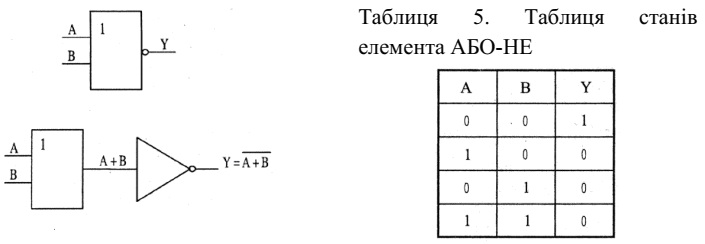

Елемент АБО-НЕ є комбінацією елемента АБО й

інвертора. Подібно

елементу І-НЕ,

елемент АБО-НЕ також може бути використаний для створення інших логічних елементів. Схематичне позначення елемента АБО-НЕ,

а також його еквівалентність послідовно

включеним елементу АБО й інвертору показані на мал. 5. Кружечок на виході

показує інвертування функції АБО.

Мал. 5. Елемент АБО-НЕ

Табл.

5 - таблиця істинності для двовходового елемента АБО-НЕ.

Помітимо, що

його вихід є запереченням

виходу елемента АБО. 1 на виході

з'являється тільки тоді, коли на обоє входу подано 0. Якщо на кожній із

входів подано 1, то на виході буде 0. Існують елементи

АБО-НЕ із двома, трьома, чотирма й вісьма входами.

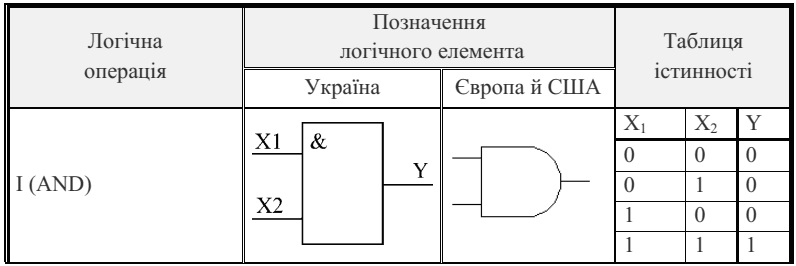

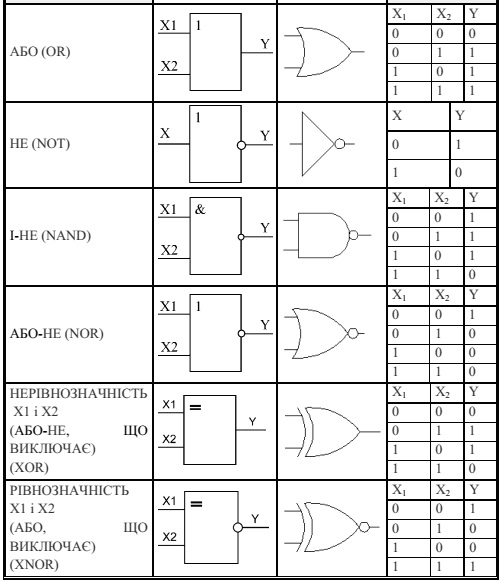

Отримані про елементи відомості систематизуємо в

таблиці 6.

Таблиця 6. Логічні елементи

4. Тригери

Тригер - це пристрій із двома стійкими станами рівноваги, призначений

для запису й зберігання

інформації. Під дією вхідних сигналів тригер

може

перемикатися з одного

стійкого стану в

інший. При цьому напруга на його

виході стрибкоподібно міняється. Число входів залежить від виконуваної

функції.

У цей час в інтегральнім

виконанні виробляється багато тригерів як у вигляді самостійних виробів, так і в складі різних

функціональних обладнань -

лічильників, регістрів, запам'ятовувальних

пристроїв і т.п. Вони мають складні електричні

схеми й різняться числом входів, способами введення

вхідної інформації, реалізованою функцією

переходів, елементною базою,

електричними й тимчасовими

параметрами, конструктивним оформленням і

іншими показниками.

В асинхронних

тригерів є тільки інформаційні (логічні)

входи.

Асинхронні тригери відрізняє властивість

спрацьовувати відразу після зміни

сигналів на входах.

У синхронних

тригерів зміни сигналів на інформаційних

входах ще

недостатньо для спрацьовування. Необхідний

додатковий командний імпульс, який подається на

синхронізуючий, або, як його частіше називають, тактуючий вхід.

Існує кілька типів тригерів.

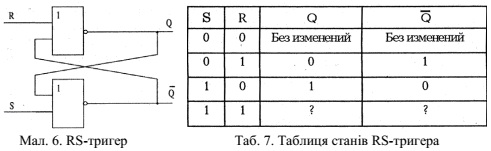

RS-тригер.

RS-тригер утворено двома перехресно зв'язаними елементами АБО-НЕ

або І-НЕ (мал. 6).

RS-тригер

має два виходи Q і Q й два керуючих входи: R (Reset -

скидання) і S (Set - установка). На виходах тригера рівні завжди протилежні:

якщо Q = 1, то Q- = 0, і навпаки.

Для того щоб зрозуміти роботу ланцюга,

припустимо, що вихід Q , вхід R

і S мають низький рівень. Низький рівень виходу Q- подається на один із входів елемента 2. На вході S також низький рівень. На виході елемента 2 високий рівень, який подається на вхід елемента 1, утримуючи його вихід на низькому рівні. Коли на виході Q з'являється низький рівень, говорять, що тригер у вихідному стані (RESET). Він залишається в цьому стані невиразно довго, доти, поки на вхід S

елемента 2 не буде поданий високий рівень. Коли на вхід S елемента 2 буде поданий

високий рівень,

на виході елемента

2 з'явитьсянизький рівень, а цей вихід зв'язаний із входом елемента 1.

Оскільки на вході R елемента 1 низький рівень, на його виході Q низький рівень зміниться на високий і подається на вхід елемента 2, забезпечуючи на виході Q низький рівень. Коли на виході Q високий рівень, говорять, що тригер в одиничному (SET) стані. Він залишається в цьому стані доти, поки на вхід R не

буде

поданий високий рівень, що переводить тригер у вихідний стан.

«Неприпустима»,

або «недозволена», умова має місце, коли одночасно на

обидва входи, R і S, подається високий рівень. У цьому випадку виходи Q й Q- намагаються

перейти в низький стан,

але Q й Q- не можуть бути одночасно в однаковому стані без порушення роботи

тригера. При одночасному відключенні високого рівня із входів R і S обидва виходи намагаються перейти в стан з високим рівнем. Оскільки логічні елементи

небагато відрізняються друг від друга, те один з них перейде в стан з високим рівнем. Це змусить інший елемент перейти в стан з низьким рівнем. У цьому випадку має місце непередбачений режим роботи

й, отже, стан виходів

тригера не може бути визначеним.

Іншим типом тригера є тригер із синхронізуючим входом.

Він

відрізняється від

RS-тригера тим, що для його роботи необхідний додатковий вхід. Третій вхід називається тактовим (або синхронізуючим). На

мал. 7 зображена логічна схема тригера із

синхронізуючим входом і його схематичне

позначення. Сигнал високого рівня на кожному із входів вхідного блоку

тригера активізує тригер, змушуючи його

змінити стан.

Вхідний блок,

називаний «керуючим елементом», направляє тактові імпульси на входи

елементів тригера.

Мал. 7. Логічна схема тригера із

синхронізуючим входом і його схематичне

позначення

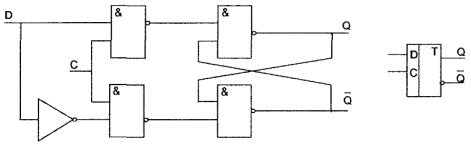

D-тригер.

У цифрових мікросхемах дуже часто застосовують

тригери з єдиним

входом даних D (data), так звані D-тригери. Вони корисні тоді, коли повинен бути збережений тільки один біт даних (1 або 0). На мал. 8 зображені логічна схема й умовна позначка D-тригера.

Він має один вхід для даних і вхід для тактових імпульсів.

Функціональна особливість цього типу тригерів

полягає в тому, що сигнал на виході Q в такті n+1

повторює значення вхідного сигналу Dn в попередньому такті n і

зберігає (запам'ятовує) цей стан до наступного такту.

Інакше кажучи, D-тригер затримує один такт інформацію, що існувала на

вході D. Тому

D-тригер також називають тригером із затримкою.

Мал. 8. D-тригер.

D-тригери, з'єднані разом, утворюють зрушувальні й

регістри пам'яті, які

широко використовуються

в цифрових системах.

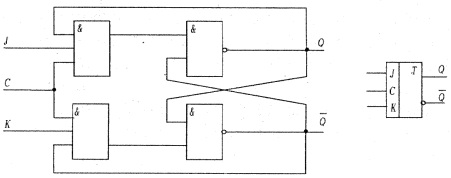

JK-тригер.

Найбільше широко використовуваний тригер -

JK-тригер - має всі особливості тригерів інших

типів. Логічна схема й позначення JK-тригера

показані на мал. 9.

Мал. 9. JK-тригер

JK-тригер при всіх комбінаціях, крім однієї J=K=1, функціонує, як RS

тригер, причому вхід J відіграє роль входу S,

а K – вхід відповідає R-входу. При вхідній комбінації J=K=1 відбувається перекидання тригера й

вихідні сигнали міняють своє значення.

JK-тригери широко використовуються в багатьох цифрових

ланцюгах,

особливо в схемах лічильників. Лічильники

можна знайти майже в кожній

цифровій системі.

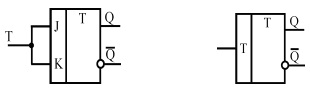

Т-тригер.

Як ми вже відзначали, при вхідній комбінації J

= K = 1 відбувається

перекидання тригера й вихідні сигнали міняють своє значення. Т-тригер

виходить при з'єднанні входів J і K в один рахунковий вхід.

T - тригер (рахунковий) - єдиний вид тригера, поточний стан якого

визначається його ж станом у попередньому такті.

Умовна позначка T

– тригера, назва якого

походить від англійського

слова toggle – перекидатися.

Мал. 10. Схема перетворення

JK-тригера в T – тригер і умовне графічне

позначення T – триггера

Асинхронні й синхронні Т - тригери

в основному застосовуються

для

рахунку числа вхідних імпульсів (звідси й назва - "рахунковий") і

для розподілу частоти

проходження вхідних імпульсів.

Тригери є основними будівельними блоками для побудови послідовних

логічних ланцюгів. Вони можуть бути з'єднані

разом і утворювати лічильники, регістри зсуву й пристрої пам'яті.